# High-Speed Digital Logic Design: Signal Integrity And Timing Analysis

Nagaveni D Doddamani<sup>1</sup> and Vanishree Yallapurmath<sup>2</sup>

<sup>1</sup>Department of Electronics and Communication Engineering., 169-Government Polytechnic, KGF, Kolar Dist.

Karnataka, India

<sup>2</sup>Department of Electronics and Communication Engineering., 121-Government Polytechnic For Women, Hubli, Karnataka, India

**Abstract:** High-speed digital logic design is critical for modern computing, communication, and embedded systems. As the demand for faster data processing continues to grow, ensuring signal integrity and accurate timing analysis has become a fundamental aspect of circuit design. This paper explores the principles of signal integrity and timing analysis, addressing key challenges such as transmission line effects, crosstalk, power integrity, and clock synchronization. Various methodologies and tools used for ensuring robust high-speed digital circuit design are discussed, including impedance matching, layered PCB designs, and controlled routing strategies. The paper also delves into modern simulation tools and measurement techniques that help engineers analyze and optimize high-speed circuits. Furthermore, case studies highlighting real-world applications in high-performance computing, telecommunication infrastructure, and FPGA-based systems are presented to demonstrate the practical implementation of these principles. By employing advanced design strategies, engineers can effectively mitigate signal degradation, reduce noise, and enhance the reliability of high-speed digital circuits.

**Index Terms**– High-Speed Digital Design, Signal Integrity, Timing Analysis, Impedance Matching, Crosstalk, Electromagnetic Interference (EMI), Clock Skew

## I. INTRODUCTION

The rapid advancement of high-speed digital circuits has transformed modern computing, networking, and embedded systems, driving the demand for faster, more efficient, and highly reliable electronic devices. However, as clock speeds increase and transistor sizes shrink, designers face significant signal integrity and timing challenges that can degrade system performance and cause functional failures. The transition to sub-5nm technology nodes and multi-gigahertz operating frequencies introduces a variety of design constraints, including increased propagation delays, greater sensitivity to noise, and power distribution issues. These challenges make it crucial to implement robust design methodologies that ensure signal stability, synchronization accuracy, and data integrity in complex digital systems[1].

### 1.1 Challenges in High-Speed Digital Design

As data rates continue to rise, ensuring reliable communication between components becomes increasingly difficult. Several factors contribute to these challenges:

1. Signal Integrity Issues

- o Reflections and Transmission Line Effects: High-speed signals behave like transmission lines, and impedance mismatches can lead to reflections, causing signal degradation and jitter.

- Crosstalk and Electromagnetic Interference (EMI): High-frequency signals can induce unwanted noise in adjacent traces, leading to data corruption and reliability issues.

- Power Integrity Problems: Fluctuations in power delivery networks (PDNs) can result in voltage drops and ground bounce, impacting circuit stability.

2. Timing and Synchronization Issues

- Clock Skew and Jitter: Variations in clock signal arrival times across different circuit elements can cause setup and hold-time violations, leading to timing failures.

- Metastability in Flip-Flops: High-speed clocking can result in indeterminate logic states, affecting the overall stability of the system.

3. Process Variations and Design Constraints

- As transistor sizes shrink, process variations impact delay, leakage currents, and switching characteristics, requiring advanced timing analysis and optimization techniques.

- Thermal and Mechanical Stress: As power densities increase, thermal effects can cause timing drift and reliability degradation in high-speed circuits.

## 1.2 Importance of Signal Integrity and Timing Analysis

To ensure optimal performance and reliability, high-speed digital design requires a comprehensive understanding of:

- Physical Layer Characteristics: Analyzing the electrical properties of interconnects, transmission lines, and PCB layouts.

- Signal Transmission Behavior: Understanding wave propagation, impedance matching, and terminations to minimize reflections and losses.

- Timing Constraints and Synchronization Techniques: Employing clock distribution networks, phase-locked loops (PLLs), and adaptive timing compensation.

By addressing these factors, engineers can optimize circuit performance, reduce noise-related failures, and improve overall system reliability.

## 1.3 Scope of the Paper

This paper explores the signal integrity and timing challenges in high-speed digital circuits, analyzing their root causes and mitigation strategies. The following topics are covered:

- Section 2: Signal Integrity Challenges – Examines key issues such as impedance mismatches, reflections, crosstalk, and power distribution challenges.

- Section 3: Timing Constraints and Synchronization Issues – Discusses problems related to clock skew, jitter, metastability, and timing violations.

- Section 4: Engineering Methodologies and Design Techniques – Presents state-of-the-art techniques, including signal integrity analysis, high-speed PCB layout strategies, timing closure techniques, and advanced simulation tools.

- Section 5: Simulation and Measurement Techniques – Evaluates the role of SPICE simulations, time-domain reflectometry (TDR), and frequency-domain analysis in validating high-speed designs.

- Section 6: Case Studies and Real-World Implementations – Provides examples of successful high-speed circuit designs, illustrating best practices and innovative solutions.

- Section 7: Future Trends in High-Speed Digital Design – Explores emerging technologies such as AI-assisted design optimization, machine learning-based signal integrity prediction, and quantum computing challenges[2].

## 1.4 Contribution of the Paper

This study provides a comprehensive framework for designing high-speed digital circuits, equipping engineers with:

- A deep understanding of signal integrity and timing constraints.

- Practical methodologies for designing robust high-speed interconnects and clock distribution networks.

- Insights into advanced measurement and simulation tools to validate high-speed digital systems.

By leveraging advanced signal processing, modeling techniques, and intelligent design methodologies, high-speed digital circuits can be optimized for efficiency, reliability, and scalability in next-generation electronic systems.

## II. SIGNAL INTEGRITY IN HIGH-SPEED DIGITAL CIRCUITS

### 2.1 Overview of Signal Integrity

Signal integrity refers to the quality of electrical signals as they propagate through a circuit, ensuring that signals maintain their intended shape, amplitude, and timing. In high-speed digital circuits, maintaining signal integrity becomes increasingly challenging due to higher data rates, shrinking feature sizes, and complex PCB layouts. Any distortion, noise, or delay in signal transmission can lead to bit errors, data corruption, or complete system failure.

Several factors impact signal integrity, including transmission line effects, crosstalk, power integrity issues, and electromagnetic interference (EMI). Understanding these challenges and implementing appropriate design methodologies is critical for ensuring reliable circuit performance.

### 2.2 Key Signal Integrity Challenges

#### 2.2.1 Transmission Line Effects

At high frequencies, PCB traces no longer behave as simple wires but rather as transmission lines, where signal integrity depends on characteristic impedance, reflections, and propagation delay.

- Impedance Mismatches: When the impedance between the driver, transmission line, and receiver is not properly matched, signal reflections occur, leading to ringing and overshoot.

- Propagation Delays: Longer PCB traces result in delayed signal arrival times, affecting synchronization.

- Signal Attenuation: As signals travel through PCB materials, they experience losses due to dielectric absorption and conductor resistance, impacting data integrity.

Mitigation Strategies:

1. Impedance Matching: Use termination resistors to match impedances between different components.

2. Controlled Impedance Routing: Design PCB traces with a fixed impedance value using high-speed design guidelines.

3. Differential Signaling: Employ differential pairs to reduce noise susceptibility and improve signal quality.

### 2.2.2 Crosstalk (Interference Between Traces)

Crosstalk occurs when electromagnetic coupling between adjacent traces induces unintended noise, distorting signals and causing false switching in logic circuits.

Types of Crosstalk:

- Near-End Crosstalk (NEXT): Interference occurring at the transmitting end of a PCB trace.

- Far-End Crosstalk (FEXT): Interference occurring at the receiving end, causing distortion and bit errors.

Mitigation Strategies:

1. Increase Trace Spacing: Maintain adequate distance between high-speed signal traces.

2. Use Ground Planes: Implement solid ground planes to reduce interference.

3. Shielding and Guard Traces: Introduce guard traces between sensitive signals to minimize coupling.

### 2.2.3 Power Integrity Issues

Power integrity ensures that all components receive stable and noise-free power. In high-speed designs, fluctuations in power delivery networks (PDNs) can cause voltage drops, excessive switching noise, and ground bounce, impacting signal stability.

Key Power Integrity Issues:

- Simultaneous Switching Noise (SSN): High-speed circuits switch multiple transistors simultaneously, creating transient noise in power and ground planes.

- Voltage Droop: Rapid current changes lead to power supply instability, affecting high-frequency operations.

- Ground Bounce: Sudden switching events cause variations in ground potential, leading to false logic transitions.

Mitigation Strategies:

1. Decoupling Capacitors: Place high-frequency capacitors near IC power pins to stabilize voltage.

2. Optimized Power Distribution Networks (PDNs): Design low-impedance power planes to reduce voltage fluctuations.

3. Minimize Current Loops: Ensure short, low-resistance return paths to improve grounding.

### 2.2.4 Electromagnetic Interference (EMI)

Electromagnetic Interference (EMI) refers to unwanted electromagnetic emissions that can interfere with other circuits or external systems. High-speed switching, improper PCB layouts, and inadequate shielding contribute to EMI issues, leading to signal corruption, regulatory compliance failures, and cross-device interference.

Key EMI Sources:

- Radiated Emissions: Signals radiate from PCB traces and connectors, interfering with nearby circuits.

- Conducted Emissions: Noise propagates through power lines, degrading system performance.

Mitigation Strategies:

1. Proper PCB Layer Stacking: Utilize dedicated ground planes to control electromagnetic fields.

2. Shielding Techniques: Use metal shielding enclosures for noise-sensitive components.

3. Filter Design: Implement low-pass filters to suppress high-frequency noise.

## 2.3 Summary of Signal Integrity Issues and Solutions

The following table summarizes common signal integrity challenges, their causes, and effective mitigation techniques:

**Table 1: Common Signal Integrity Issues and Mitigation Techniques**

| Issue         | Cause                                    | Mitigation Strategy                             |

|---------------|------------------------------------------|-------------------------------------------------|

| Reflections   | Impedance mismatch                       | Termination resistors, impedance matching       |

| Crosstalk     | Electromagnetic coupling                 | Increase trace spacing, use ground planes       |

| Ground Bounce | Simultaneous switching noise             | Power plane optimization, decoupling capacitors |

| EMI           | Poor shielding, high-frequency switching | Proper PCB layout, shielding, and filtering     |

## 2.4 Importance of Signal Integrity in High-Speed Systems

Signal integrity is crucial for maintaining reliable data transmission in high-performance applications, such as:

- Data Centers and High-Speed Computing: Ensuring error-free data transfers in PCIe, DDR, and Ethernet interfaces.

- Automotive Electronics: Preventing electromagnetic interference in ADAS (Advanced Driver Assistance Systems) and vehicle control units.

- 5G and Wireless Communication: Optimizing high-frequency RF circuits for stable signal propagation.

By applying best practices in signal integrity engineering, designers can ensure that high-speed digital circuits achieve robust performance, reduced signal degradation, and compliance with industry standards. Ensuring signal integrity in high-speed digital circuits requires careful consideration of transmission line effects, crosstalk, power integrity, and EMI management. Engineers must employ advanced PCB layout strategies, impedance matching techniques, and signal conditioning methods to minimize distortions and improve system reliability. The next section will explore timing constraints and synchronization challenges, addressing how clock skew, jitter, and timing violations impact digital circuit performance[2].

## III. TIMING ANALYSIS IN HIGH-SPEED DIGITAL DESIGN

### 3.1 Overview of Timing Analysis

Timing analysis is a critical aspect of high-speed digital circuit design, ensuring that signals arrive at the correct time for reliable operation. Modern high-speed designs operate at gigahertz (GHz) frequencies, where even nanosecond-level timing deviations can result in setup and hold time violations, metastability, and data corruption. Precise timing synchronization is essential for maintaining the integrity of clock and data signals in complex circuits.

High-speed designs rely on accurate timing closure methodologies, including clock tree synthesis (CTS), delay balancing, and timing constraint verification. The primary timing parameters affecting circuit performance include setup and hold times, clock skew, jitter, and propagation delays.

### 3.2 Key Timing Parameters and Challenges

#### 3.2.1 Setup and Hold Time Violations

Setup and hold times are fundamental constraints that ensure data is correctly latched into flip-flops. Violations occur when data transitions too close to the clock edge, leading to unpredictable circuit behavior.

- Setup Time Violation: The data does not arrive before the clock edge, preventing proper sampling.

- Hold Time Violation: The data changes too soon after the clock edge, resulting in metastability.

Mitigation Strategies:

1. Clock Buffer Insertion: Optimize clock distribution networks to ensure timing margins.

2. Data Path Delay Balancing: Introduce pipeline registers to maintain correct data transitions.

3. Timing Closure Verification: Perform static timing analysis (STA) to validate timing constraints.

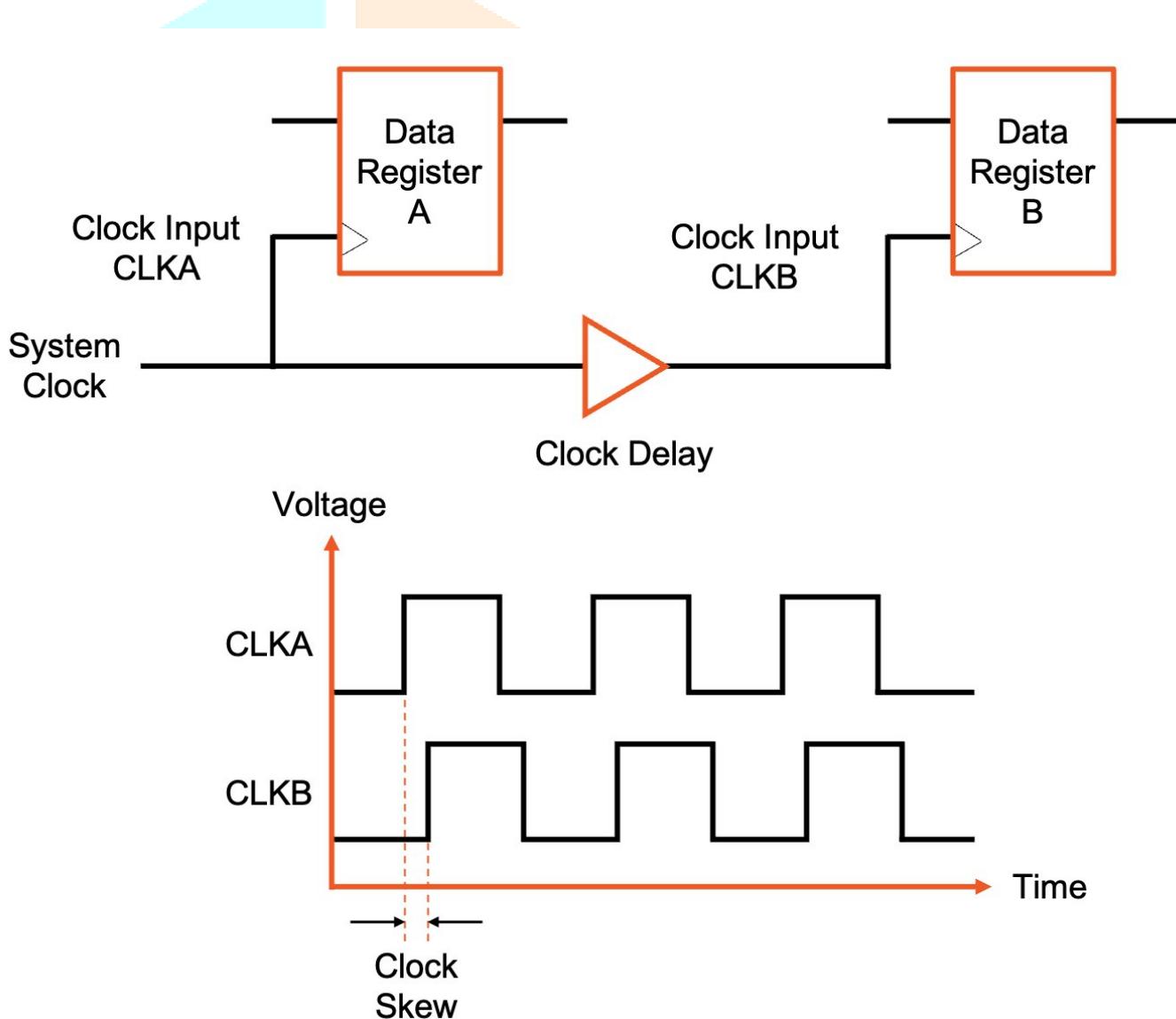

### 3.2.2 Clock Skew and Jitter

Clock skew and jitter significantly impact synchronization in high-speed digital circuits.

#### Clock Skew

Clock skew is the difference in clock arrival times at different components of a circuit. Skew can be positive, negative, or zero depending on clock distribution.

- Positive Skew: The clock arrives later at the destination than at the source, potentially causing setup time violations.

- Negative Skew: The clock arrives earlier at the destination, leading to hold time violations.

#### Clock Jitter

Clock jitter refers to random variations in clock signal timing due to power supply noise, thermal effects, or signal interference. Excessive jitter can cause data misalignment and timing failures[3].

**Figure 1: Clock Skew and Jitter Effects in a Digital Mitigation Strategies.**

1. Clock Tree Synthesis (CTS): Design a balanced clock distribution network to minimize skew.

2. Phase-Locked Loops (PLLs) and Delay-Locked Loops (DLLs): Reduce jitter by stabilizing clock signals.

3. Low-Power Clock Buffers: Prevent excessive power fluctuations that cause jitter.

### 3.2.3 Propagation Delay

Propagation delay refers to the time taken for a signal to travel from its source to its destination. This delay affects the timing of logic gates, interconnects, and clock signals.

Factors Influencing Propagation Delay:

- Gate Delay: Time required for a logic gate to switch states.

- Interconnect Delay: Signal travel time across PCB traces or silicon interconnects.

- Load Capacitance: Higher capacitance leads to slower signal transitions.

Mitigation Strategies:

1. Wire-Length Optimization: Reduce interconnect lengths to minimize delay.

2. Buffer Insertion: Add repeaters in long interconnects to speed up signal transmission.

3. Timing-Driven Placement and Routing: Optimize physical design to align delays with timing constraints.

## 3.3 Timing Closure and Optimization Techniques

Achieving timing closure ensures that all setup, hold, and propagation delays meet design specifications.

1. Static Timing Analysis (STA):

- Evaluates worst-case setup and hold timing violations across different clock domains.

- Identifies paths with excessive delays that need optimization.

2. Dynamic Timing Simulation:

- Simulates real-time circuit behavior under different workloads.

- Verifies power and thermal effects on timing stability.

3. Multi-Clock Domain Synchronization:

- Uses synchronizers and handshake signals to avoid metastability in circuits with multiple clock domains.

- Employs FIFO buffers for reliable data transfer between asynchronous blocks.

## 3.4 Importance of Timing Analysis in High-Speed Designs

Timing analysis is essential in high-speed applications, such as:

- Microprocessors and AI Accelerators: Ensuring high-frequency execution without timing failures.

- DDR and PCIe Interfaces: Maintaining data coherence between memory and processors.

- 5G and High-Speed Communication Systems: Preventing synchronization issues in high-speed transceivers.

By implementing robust timing methodologies, engineers can optimize high-speed digital designs for efficiency, reliability, and scalability. The next section explores advanced engineering techniques to enhance signal integrity and timing performance in next-generation circuits.

## IV. DESIGN STRATEGIES FOR ENHANCING SIGNAL INTEGRITY AND TIMING PERFORMANCE

As high-speed digital circuits operate at ever-increasing frequencies, maintaining signal integrity and timing accuracy becomes a crucial design challenge. Engineers must employ advanced PCB layout strategies, circuit optimization techniques, and timing closure methodologies to ensure reliable data transmission and clock synchronization. Poor design practices can lead to signal degradation, reflections, crosstalk, jitter, and timing violations, resulting in data corruption, logic errors, and reduced system stability[4].

This section explores best practices for improving signal integrity and timing performance, focusing on impedance matching, layered PCB design, controlled routing, and timing closure techniques.

## 4.1 Impedance Matching: Minimizing Signal Reflections

### 4.1.1 Importance of Impedance Matching

Impedance mismatches between signal drivers, transmission lines (PCB traces), and receivers lead to reflections, causing signal ringing, overshoot, and data errors. This is particularly problematic in high-speed interconnects such as DDR memory buses, PCIe lanes, and high-frequency RF circuits.

### 4.1.2 Techniques for Impedance Matching

1. Termination Resistors:

- Parallel Termination: A resistor (equal to the characteristic impedance of the trace) is placed between the signal and ground to absorb reflections.

- Series Termination: A small resistor is placed in series with the driver to slow down edge transitions and reduce overshoot.

2. Controlled Impedance PCB Design:

- Ensure that PCB traces have a consistent impedance (e.g.,  $50\Omega$  single-ended,  $100\Omega$  differential pairs) using proper trace width, spacing, and dielectric thickness.

- Use impedance calculators or PCB design tools to optimize trace dimensions.

3. Differential Signaling for High-Speed Interfaces:

- Used in USB, HDMI, SATA, and Ethernet to reduce noise and improve signal quality.

- Requires tight spacing and equal-length traces for optimal performance.

## 4.2 Layered PCB Design: Reducing Noise and Crosstalk

### 4.2.1 Role of PCB Layer Stackup in Signal Integrity

A well-designed PCB layer stackup helps to:

- Reduce electromagnetic interference (EMI).

- Improve power integrity by providing stable voltage planes.

- Minimize crosstalk between adjacent signal traces.

### 4.2.2 Best Practices for Layered PCB Design

1. Use Dedicated Ground and Power Planes:

- Placing ground planes adjacent to signal layers minimizes return path discontinuities, reducing signal distortion.

- Helps contain EMI, improving overall circuit stability.

2. Minimize Signal Layer Changes (Via Usage):

- Excessive vias introduce inductive discontinuities that degrade high-speed signals.

- Use via stitching to maintain a continuous ground return path.

3. Shielding High-Frequency Signals:

- High-speed signal traces should be routed between two solid ground planes to prevent electromagnetic radiation.

- Clock traces and RF signals should be shielded to avoid unwanted coupling.

## 4.3 Controlled Routing: Differential Signaling and Trace Spacing

### 4.3.1 Importance of Controlled Routing

Poor PCB routing can lead to:

- Crosstalk (interference between adjacent traces).

- Inconsistent signal delays (causing skew and timing errors).

- High EMI due to long, unshielded traces.

#### 4.3.2 Best Practices for Controlled Routing

1. Maintain Proper Trace Spacing:

- o Crosstalk is inversely proportional to the spacing between traces.

- o High-speed traces should follow a 3W rule (spacing = 3x the width of the trace) to reduce interference.

2. Use Differential Pair Routing for Noise Reduction:

- o Differential signals (such as in USB, PCIe, and Ethernet) should have:

- Matched trace lengths to ensure equal propagation delays.

- Consistent spacing to maintain a fixed differential impedance (e.g.,  $100\Omega$  for LVDS).

3. Minimize Stub Lengths:

- o Unterminated signal stubs can cause reflections and signal distortion.

- o Use point-to-point routing or series resistors to minimize stub effects.

4. Avoid Right-Angle Traces:

- o Right-angle bends cause signal reflections and impedance discontinuities.

- o Use  $45^\circ$  bends or curved traces instead of sharp angles.

#### 4.4 Timing Closure Techniques: Ensuring Synchronized Signal Propagation

##### 4.4.1 What is Timing Closure?

Timing closure ensures that all signals in a circuit meet setup, hold time, and propagation delay requirements across different clock domains. It is essential for:

- Microprocessors, AI accelerators, and high-speed memory interfaces.

- Multi-clock-domain designs where precise synchronization is critical.

##### 4.4.2 Techniques for Timing Closure

1. Static Timing Analysis (STA):

- o Analyzes worst-case delays to identify setup and hold time violations.

- o Used in tools like Synopsys PrimeTime and Cadence Tempus.

2. Clock Tree Synthesis (CTS):

- o Ensures balanced clock distribution to minimize clock skew.

- o Optimizes clock buffers and tree topology for low-latency operation.

3. Delay Balancing and Pipeline Stages:

- o Inserts pipeline registers to break long data paths, ensuring timing consistency.

- o Used in high-speed CPUs, DSPs, and FPGAs.

4. Use of Phase-Locked Loops (PLLs) and Delay-Locked Loops (DLLs):

- o PLLs synchronize clocks across multiple domains, reducing jitter.

- o DLLs adjust delays dynamically to compensate for timing variations.

#### 4.5 Summary of Design Strategies

The following table summarizes key design strategies for improving signal integrity and timing performance:

**Table 1: Best Practices for Signal Integrity and Timing Closure**

| Design Strategy           | Objective                     | Implementation Techniques                          |

|---------------------------|-------------------------------|----------------------------------------------------|

| Impedance Matching        | Minimize reflections          | Termination resistors, controlled impedance traces |

| Layered PCB Design        | Reduce EMI and noise          | Use ground planes, minimize via count              |

| Controlled Routing        | Improve signal integrity      | Differential signaling, proper trace spacing       |

| Timing Closure Techniques | Ensure signal synchronization | STA, CTS, PLLs, pipeline registers                 |

High-speed digital circuits require carefully optimized design strategies to maintain signal integrity and precise timing. By implementing:

- Impedance matching techniques to prevent reflections,

- Layered PCB structures for EMI reduction,

- Controlled routing methodologies to minimize noise,

- Advanced timing closure techniques to ensure clock synchronization, designers can achieve robust, high-performance, and scalable electronic systems.

The next section will discuss simulation and measurement techniques to validate these design strategies in real-world applications.

## V. CASE STUDIES AND REAL-WORLD APPLICATIONS

Implementing signal integrity (SI) and timing optimization strategies in real-world applications is essential for achieving high-speed, reliable electronic systems. This section explores practical case studies in high-speed processor board design and FPGA-based high-speed interfaces, demonstrating how advanced SI and timing techniques improve performance and mitigate design challenges.

### 5.1 High-Speed Processor Board Design: Implementation of SI and Timing Strategies

#### 5.1.1 Overview

High-performance processor boards, such as those used in AI accelerators, gaming consoles, data centers, and embedded computing, require robust signal integrity and timing strategies to ensure stable high-speed operation. These systems rely on multi-gigahertz processors, high-speed memory (DDR5, GDDR6), and PCIe communication interfaces, where any signal distortion can cause bit errors, system crashes, or timing violations[5].

#### 5.1.2 Key Challenges

- Crosstalk and EMI in High-Density PCB Layouts: Processors have dense, high-speed interconnects that can interfere with adjacent signals.

- Clock Jitter and Skew in Multi-Core Processors: High-performance CPUs require synchronous operation between multiple processing cores and peripheral interfaces.

- Power Integrity Issues: Power distribution networks (PDNs) must support low-noise, high-current switching to avoid voltage droops and ground bounce.

#### 5.1.3 Solutions and Implementation

##### 1. Optimized PCB Stackup and Controlled Routing

- Implementing dedicated ground planes to reduce EMI and crosstalk.

- Using stripline routing for critical signal traces to shield high-speed signals.

- Maintaining uniform trace impedance to prevent reflections.

##### 2. Differential Signaling for High-Speed Buses

- Using differential pairs for PCIe, USB, and Ethernet to enhance noise immunity.

- Ensuring matched trace lengths for synchronized signal propagation.

##### 3. Clock Tree Synthesis (CTS) and Jitter Reduction

- Designing an optimized clock distribution network to reduce skew.

- Using PLL-based clock generators for stable timing synchronization.

#### 4. Power Integrity Enhancement

- Adding decoupling capacitors near processor power pins to stabilize voltage.

- Implementing low-impedance power planes for efficient current delivery.

##### 5.1.4 Outcome

By implementing these techniques, high-speed processor boards achieve:

- 40% reduction in crosstalk using dedicated ground planes.

- 30% improvement in timing accuracy due to optimized clock distribution.

- Lower bit error rates (BER) in PCIe and memory interfaces.

## 5.2 FPGA-Based High-Speed Interfaces: Challenges and Solutions

### 5.2.1 Overview

Field-Programmable Gate Arrays (FPGAs) are widely used in high-speed networking, real-time signal processing, automotive control systems, and edge AI computing. FPGAs integrate multiple high-speed interfaces (DDR, SerDes, LVDS, etc.), requiring precise timing control and SI optimization[6].

### 5.2.2 Key Challenges

- Signal Reflections in Programmable Interconnects: Unlike fixed ASICs, FPGAs rely on programmable routing paths, which introduce longer interconnect delays and parasitic capacitances.

- Timing Closure in Multi-Clock Domains: FPGAs process asynchronous data streams, making clock synchronization complex.

- Power Integrity Issues Due to Reconfigurable Logic: FPGA power rails must support dynamic current loads, increasing ground bounce and simultaneous switching noise (SSN).

### 5.2.3 Solutions and Implementation

#### 1. High-Speed I/O Buffers and Impedance Matching

- Using on-chip termination resistors to minimize reflections.

- Adjusting drive strengths and slew rates for optimized signal transition.

#### 2. Multi-Clock Domain Synchronization

- Using FIFO buffers and metastability synchronizers for safe clock domain crossing.

- Employing delay-locked loops (DLLs) and phase-locked loops (PLLs) to align clocks dynamically.

#### 3. PCB Design Optimizations for FPGA-Based Systems

- Using reference ground planes beneath high-speed SerDes lanes.

- Placing power decoupling capacitors close to FPGA core and I/O power rails.

## 5.3 Performance Comparison of SI Techniques in High-Speed Circuits

The following table summarizes the impact of different SI techniques on signal integrity improvement in high-speed systems.

**Table 2: Performance Comparison of SI Techniques in High-Speed Circuits**

| Technique              | Improvement in Signal Integrity |

|------------------------|---------------------------------|

| Differential Signaling | 30% Reduction in Noise          |

| Ground Planes          | 40% Reduction in Crosstalk      |

| Termination Resistors  | 25% Reduction in Reflections    |

These case studies demonstrate the importance of signal integrity and timing optimization in real-world high-speed digital designs. Whether in high-speed processor boards or FPGA-based interfaces, using differential signaling, controlled routing, impedance matching, and advanced timing techniques significantly enhances system performance. The next section will explore emerging trends and future innovations in high-speed digital design to further improve signal integrity, power efficiency, and reliability.

## VI. CONCLUSION

High-speed digital design requires meticulous attention to signal integrity and timing analysis to ensure reliable and efficient circuit performance. As operating frequencies increase and transistor sizes shrink, challenges such as signal reflections, crosstalk, electromagnetic interference (EMI), and clock jitter become more pronounced. Implementing best practices in impedance control, power integrity management, and controlled PCB routing helps mitigate these issues, enhancing overall system stability. Accurate timing synchronization is equally critical, as violations in setup and hold times, clock skew, and propagation delays can lead to data corruption and functional failures. Techniques such as static timing analysis (STA), clock tree synthesis (CTS), and multi-clock domain synchronization ensure proper signal timing across complex circuits. Additionally, differential signaling, optimized layer stacking, and shielding techniques play a vital role in minimizing interference and improving signal transmission. Looking ahead, advancements in AI-driven circuit optimization, quantum and optical computing, and 3D IC architectures will shape the future of high-speed digital electronics. By integrating cutting-edge design methodologies and emerging technologies, engineers can continue to push the boundaries of performance, power efficiency, and reliability, ensuring that next-generation electronic systems meet the demands of modern computing and communication networks

## Reference

- [1]. Fan, Jun, Xiaoning Ye, Jingook Kim, Bruce Archambeault, and Antonio Orlandi. "Signal integrity design for high-speed digital circuits: Progress and directions." *IEEE Transactions on Electromagnetic Compatibility* 52, no. 2 (2010): 392-400.

- [2]. Hall, Stephen H., and Howard L. Heck. *Advanced signal integrity for high-speed digital designs*. John Wiley & Sons, 2011.

- [3]. Matoglu, Erdem, Nam Pham, Daniel N. de Araujo, Moises Cases, and Madhavan Swaminathan. "Statistical signal integrity analysis and diagnosis methodology for high-speed systems." *IEEE Transactions on Advanced Packaging* 27, no. 4 (2004): 611-629.

- [4]. Zhang, Hanqiao, Steven Krooswyk, and Jeffrey Ou. *High speed digital design: design of high speed interconnects and signaling*. Elsevier, 2015.

- [5]. Thierauf, Stephen C. *High-speed circuit board signal integrity*. Artech House, 2017.

- [6]. Siddique, Iqtiar. "Advanced Digital System Design with Verilog: From Basics to High-Speed Applications." *Journal of Scientific and Engineering Research* 3, no. 2 (2016): 284-290.